���Ƕ��ʽ�����ԃr�� ԓ����x���m̎�������ļܘ�

�r�g��2016-05-23 ��Դ��δ֪

���Ƕ��ʽ�����ԃr�� ԓ����x���m̎�������ļܘ�

�r�g��2016-05-23 ��Դ��δ֪

�F�A�ΰ댧�wоƬ�̶����ARM��̎�������ģ�����������̎�������������ȮaƷ��ARM�ĺ��Ŀɷ֞�A��R��M����ϵ�У����в�ͬ���ܣ����оƬ��Ҳ���������ʵ��Ј���������������Iϵ�y�Ȳ�����x���^�m�ϵĺ��ģ����������ԃr�ȼѵĮaƷ��

�F��Ƕ��ʽ���Ã���õ��T��̎��������˰댧�w�S��Ҳ�e�OͶ�벼�֣��e�����f���\(ARM)��̎������V��������Ƕ��ʽ�I��ARM Cortex-Aϵ��̎��������ʹ������Ҫ������Iϵ�y(Rich OS)���Ч�ܵđ����У�Cortex-Rϵ��̎���������^�ѵļ��rЧ�ܣ�Cortex-Mϵ��̎�����t��������������͵�С�͑��á�

Ŀǰ ����Cortex-M�ĮaƷ�������w�dz����ӻ����x헣��������OӋС�ɡ����ĵ͵�Cortex-M0����ʹ�������Ƕ�롢���ɱ����еđ������ǻ��Мy�� ���c�ϣ��������ڴ��Ј�����������Cortex-M3��Cortex-M4���ѵĄt��Cortex-M7����߂���ߵ�Ч�ܣ����Ԉ����ܼ��\��Ĺ� ��ؓ�d������Ӎ̖̎���ȡ�

Cortex-M̎�������õ�ARMv6-M��ARMv7-M�ܘ����Ǹ��麆����߉���ij�ʽ�OӋģ�ͣ����麆��ʹ�����OӋ��̎�������ı������O�����^���ԣ��܉����ڸ����ӻ��Č�����

�mȻCortex-M���ĵĺ����Ԍ��ֵ�Ƕ��ʽ���Á��f���^�ѵă��ݣ�����������������Ҫ����ܡ�Ч�ܸ��ߵĭh���������ͬ����ҕЧ�ʺͺ�������� ������ҪLinux��Android����͵�ƽ�_���Iϵ�y�����ô���͵����Iϵ�y���t�܉�ʹ�Ñ��÷������V�����߶���ҏ��s��ܛ�w���Bϵ�y���_�l�µ��� �C��

Cortex-M̎�������OӋ����ᘌ��@Щ���A�����Iϵ�y�����δ����������Ҫ���ض���Ҫ���ܡ��e�����f���@Щ̎����δ�߂�ӛ�� �w�����Ԫ(MMU)���ڟo��֧Ԯ̓�M�惦���h������r�£���ȻҲ�Ͳ�֧Ԯ�@һ����Iϵ�y����ij헑�����Ҫ����ܵ����I�h�������x��ͨ�����^��Ч�ʵ� Cortex-A���ġ��@Щ�����ṩƽ�_���Iϵ�y������^�M�A���ܣ�ͬ�r���ஔ��ҕ���ģ����w���f�Ǹ�����A�ҏ��Ի��ij�ʽ�OӋģ�͡�

���b�ڴˣ�ARM Cortex-A̎�����ಿ���ڸ��N���Ƕ��đ��ã�����������ҪLinux������������Iϵ�y���Ј���

�D1�@ʾCortex-A̎����Ŀǰ�đ��÷��������c�������е��^���ĺ��ġ������Դ�һϵ���е�����Cortex-A32̎����������

�D1��Cortex-A̎�����c�ܘ�

Cortex- A32���M��Cortex-Aϵ���^��������T���������Ҫ������Iϵ�y�h�������Cortex-A̎�������ṩ��Ч�ܼ������Ы@��đ��á�ԓ̎���� ��Ŀǰ���е��ĵ�ARMv8-A̎�������鴩��ʽ�b�á����W(IoT)�Ͷ��Ƕ��ʽ���ã���������ҪLinux�@һ�ƽ�_���Iϵ�y֮���õ��^���x ��

����32λԪ�\���Ј���Aϵ����̎�������ĸ���

Cortex-A32��ARM�ܘ��а��������صĽ�ɫ�������ARMv8-A�ܘ������H֧Ԯ32λԪ���\�㡣�D2�@ʾCortex-A32�������ARMv8-A�ܘ��O�����Լ��cCortex-A35�IJ��

�D2��Cortex-A32�cCortex-A35���^

Cortex- A35ͬ�r����32λԪ��AArch32��64λԪ��AArch64�ɷN���Р�B���܉������ṩARMv8-A�ܘ���64λԪ���ܡ���һ�� �棬Cortex-A32�tֻ����32λԪ��AArch32���Р�B���Ƴ���64λԪ�Ĺ����Ժ��H�w�e�s�p�����ڲ���Ҫ64λԪ���ܵ�ʹ�Á��f������ �����书�ġ��M��Ƕ��ʽ�I�������S�����ö��ɏ�64λԪ�Ĉ����Ы@�棬�����S����������32λԪ���Ҍ��ڿ��AҊ��δ�����֬F�r�����@Щ���ñ��� Cortex-A32��Ŀ���Ј���

AArch32���Р�B������ڵ�Cortex-A̎���������õ�ARMv7-A�ܘ����M���档���˽⣬Cortex-A32��ʹ���߂�64λԪ�Ĺ��ܣ������ṩijЩ��Ҫ�ď�������˹���߀�ǃ���Cortex-A7��Cortex-A5��

���⣬�����Բ����@Щ�f��ARM̎�����������OӋ�����Դ���ͬ�Ј���Ŀ�˵����OӋ���ԣ�Cortex-A32���������x��

AArch32����ARMv7-A�����c������

.�����S����ָ��������㹦��Ч�ܸ���

.�¼���Load Acquire��Store Releaseָ��ṩ����Ч�ʵĴ惦�������ܣ������µ�C++11�惦�������Z��

.�~��ļ����cSIMD���cָ��

.�V����ϵ�y����ָ��

�@Щ�~����ṩ���ѵ�Ч�ܣ������f��32λԪARMv7-A̎������

Cortex-A32�R���Ž�����������Mͬ���Uչ(ACE)�������ͨ�^Cortex-A32��������ȫͬ���Ķ���̎��ϵ�y���������Ҫ�ĸ���Ч�ܡ�

������g����������Ҫ�����ƣ�Cortex-A32Ҳ��׃�w�汾���eᘌ���̎�������üѻ���ʡ�Ի��B߉���Թ�ʡ����Ĺ��ġ�

Cortex-A32�^Large Physical Address Extension(LPAE)�U���˶�ַ���w�惦�����g����ԽCortex-A5���ṩ��32λԪ(4GB)���g�����ṩ40λԪ��ַ���g��

���ı���Ҳ����������������ڸ��ƹ��ĵ��M�A���ܣ����������Ի����Դ�����������ֲ�������^��ʹ�ñ��湦���l����

ARMv7-M�cARMv8-A AArch32�ܘ����^

���Č����^ARMv7-M�cARMv8-A AArch32�ļܘ���ɫ�c���

ARMv7-M�ܘ���ɫ

ARM Cortex-M̎����ϵ����ARMv7-M�ܘ��O����Cortex-M0��Cortex-M0+�t������Ƶ�ARMv6-M�ܘ���

�˼ܘ��c��ǰ��ARM�ܘ����S�ͬ����ɫ���ҽ��^�����OӋ����֧Ԯ���Ƕ�롢�ͳɱ��ļ��r���������á������Ƴ����f�ܘ����S��ܣ���Ҳ�����¹��ܣ������һ��������������ij�ʽ�OӋģ�͡�

�e�w���f�����f��̎����(���dz�Ҋ��ARM7TDMI)��׃�ӿɿ��Y���£�

.���Iģʽ�Ĕ������߂����ϴ���p�ٵ��ɂ���Handlerģʽ��Threadģʽ������һ�ģʽ(Handlerģʽ)���x���ԃ��ș��ޡ�

.�������n���^�������mȻ�_�Ź���ʽ�OӋ�ˆTʹ�õĕ�������������ͬ����ʮ�������f�ͼܘ������õĂ�ݕ��������ƙC��Ҳ����p�٣����ֻ��Stack Pointer(r13)���ڃɂ����Iģʽ�м��ԕ��档��ݕ��������x����ʹ�ã���������ʡ�ԡ�

. ���׃�����ڮ���ģʽ������һ������������ÿ��ܕ��д�����оƬ��߅�Д࣬���Ԙ˜ʵij��������Д������(Nested Vectored Interrupt Controller�� NVIC)Ҏ��������ڼܘ��У����е�Cortex-M���ľ�����ԓҎ��ͬ�ӵأ�����̎��ģʽ���ڰ���̎����ʽλַ���������ϼ��Ԙ˜ʻ������ݵă����c �؏����I��ȫ��Ӳ�w�ό��������������Д�̎����ܛ�w��������˿��ڌ����r�_���dz����ҿ��A�y���Д����t�r�g��

.ARMv7-M���x�x���ԵĴ惦�����o�ܘ���ԓ�ܘ��cijЩ�f��ARM̎�������õļܘ���ơ���Cϵ�y���ڼ��r���Iϵ�y(RTOS)���\����ϵ�y����ͨ������Ҫ̓�M�惦������˲�֧Ԯ̓�M�惦����

.��֧Ԯ���N���r���Iϵ�y���\���͈��У���Щ�˜ʵ�оƬ��߅Ҳ���ڼܘ��м��Զ��x����SysTick Timer��

.��sС̎�������ĵĴ�С��ARMv7-M̎�������\���s��ֻ��Thumbָ�(����Thumb-2����)���H����С���Ӽ����M�����FС�ĺ��ġ�

ARMv8-A AArch32��ɫ

Cortex- A̎��������ARMv7-A��ARMv8-A�ܘ��O����ARMv8-A̎�����ṩAArch32���Р�B����32λԪARMv7-A�ܘ������������ݻ� �档�@Щ�ܘ��Ɍ��F���T�OӋ�Á�֧ԮLinux��Android��Windows��ƽ�_���Iϵ�y�Ĺ��ܣ����@Щϵ�y��Ҫ̓�M�惦���h����

���cCortex-M̎�������Ľ�Ȼ��ͬ���ض����ܰ�����

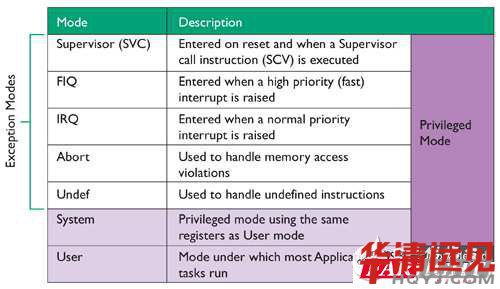

. ���߂����ϵ����Iģʽ��User��Supervisor�����Ҫ��(IRQ)�������Д�(Fast Interrupt�� FIQ)��Undefined��Abort��System��ÿһģʽ������̎���ض�����¼�(����IRQģʽ�����OӋ����̎��IRQ�Д�)�� AArch32��֧ԮHyp��Monitor�@�ɂ��~���ģʽ���@�ɂ�ģʽ�քe����̓�M����ARM TrustZone���g��

.���˿��õĵ�䛔�����ͬ(16)��AArch32߀���S���c�������Iģʽ���P��“���”���������M�����P�����Iģʽ�r���@Щ��������ȡ��Userģʽ�µĕ���������˿ɺ����S�ஐ��̎����������Ҳ��ʾ�C���Ĺ����ͳ�ʼ�����������ӡ�

.�䮐��ģʽ�O�鲻ͬ����ԭ�ʹ��������ARM�ܘ��b���С����w���f������������һ�M�Ɉ��е�ָ���������λַ���҃��ݵă����c�؏�Restore��������ȫ���o��ʽ�OӋ�ˆT���С�

.��IJ�Ǽ����˴惦�������Ԫ���Ɉ��к������˰l֮̓�Mλַ���Լ��惦��ϵ�y����Ҫ�Č��wλַ�g���D�g����˱��܌�����ȫ���S�x���̓�M�惦���h�����Թ�Linux��ƽ�_���Iϵ�yʹ�á�

ARMv7-M�cAArch32�IJ

�IJ���Cortex-M̎������ϵ�y�D�Q������Cortex-A32̎�����r�����S���¹���ֵ���Pע��

�mȻ�@�ɷN�ܘ����S�����֮̎(���ݕ�������ָ�֮�g���S����ͬ�c)������Ҫ����ARMv8-A�ܘ���AArch32���Р�B�������S��ܣ��������f�ͼܘ��Ĺ��ܞ���A��

�����f��AArch32���߂䣬����ARMv7-M���o���O��Ĺ��ܡ�

���Iģʽ

�� �D3��ʾ��ARMv7-Mֻ���x�ɂ����Iģʽ��Threadģʽ�cHandlerģʽ�����o��Ҫ��Handlerģʽ���x����ȡ�����ș��ޣ��mȻ�@헹��� δ���Ҫ��ܛ�w��ʹ�á�Handlerģʽ�m����̎��������Threadģʽ�t����ʹ����̎�������@�ɂ�ģʽ�D�Q���������Ԅӵģ������ض��¼��°l���� ��D3��ʾ�����磬�l�������r���Ԅ��M��Handlerģʽ������̎����ɕr�t���˳�Handlerģʽ��SVCallָ�����Ҫ�ķ�����ܛ�w������M�� Handlerģʽ(Ҳ�Ɍ����õ�IRQ�O�����̎����B���Ԉ���Handler)��

�D3��ARMv7-M���Iģʽ

�D4�t�@ʾAArch32���Р�B֧Ԯ�����Iģʽ���cARMv7-M���^��AArch32���߂�����ģʽ�������傀ָ������̎���ض����������磬ȡ��FIQ�����r���M��FIQģʽ;���l��δ���xָ������Σ����M��Undefģʽ��

�D4��AArch32���Iģʽ

ģʽ���D�Qͨ�����ԄӰl������Ҳ����Current Program Status Register(CPSR)�Ќ���Mode��λ����ܛ�w���Ɓ������ГQģʽ���会���������¡��cSVCallָ����ƣ�SVCָ������ܛ�w���lSVC�������M��SVCģʽ��

�D4��δ�@ʾAArch32��֧Ԯ����ɂ�ģʽ(�鹝ʡ���g)��Ҳ����Hypģʽ(����Hypervisor)�cMonitorģʽ(����TrustZone��ȫ��)�����P���}�^����s�����IJ���ӑՓ��

��ݕ�����

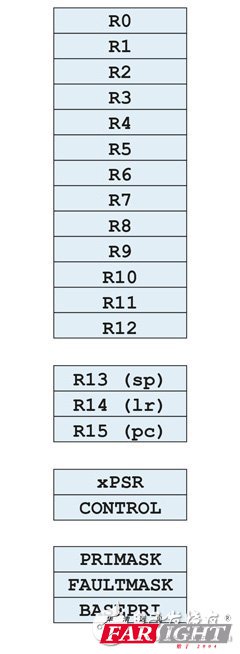

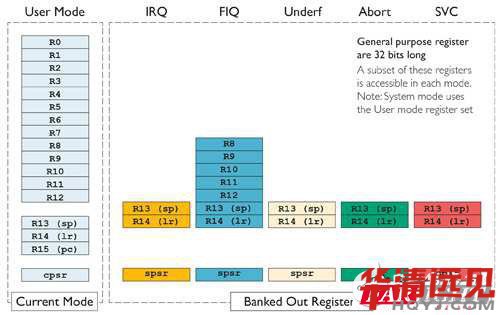

�D5�@ʾARMv7-M��AArch32�Ă�ݕ��������ɿ������S���������鹲�У�����@�ɷN�ܘ��������u��ARMv6����ǰ�ļܘ���

�D5��ARMv7-M��䛼�

����ָ��ɴ�ȡʮ����ͨ���͵ĕ�����r0-r12�����@�ɷN�ܘ��У�r13������Stack Pointer(SP)��r14������Link Register(LR)��r15�t������Program Counter(PC)����ARMv7-M�У��@Щ���╺�����Ĵ�ȡ�H����ijЩ��ӳ�@Щ���������ܵ��ض�ʹ�à�r;��AArch32�У��@Щ�������Ĵ�ȡ �t����κ�����ͨ�õĕ�����(�mȻ׃��Program Counter�Ĕ�ֵ������ɷ��A�ڵĸ�����)��

ARMv7-Mָ��С�����~��������;�ĕ�����PRIMASK��FAULTMASK��xPSR��CONTROL��BASEPRI�����ڿ��Ƽ��O��̎�����������ڹ�������̎����

ָ�

�D 5�c�D6�քe��ARMv7-M�cAArch32��䛼���������^�ɿ���AArch32Ҳ�ṩ�S���c�ض����Iģʽ�P�ĕ��������@Щ�����������M�����P��ģ ʽ�r�c����Userģʽ�µĕ��������Q�������ٔ�����ָ�����ָ����o����ȡ�@Щ����������Ҳ�o��ֱ�Ӵ�ȡ���䔵ֵ��ģʽ׃���r����������������̎���� ����ÿ������ģʽ�����Լ��Č���SP��ÿ�����������ڪ����ĶѯB��̎������ˮ���̎���ij�ʽ�OӋ���鷀���Ұ�ȫ��ȡ�î����r�����Pģʽ�µ�LR�O���鮐�� ����λַ��

�D6��AArch32��䛼�

ÿ������ģʽ�����F��߀�н�SPSR���~�╺������SPSR�������M������rȡ��ĿǰCPSR��ֵ�Ŀ��գ�����LRʹ���£����ṩ�Ԅӻ��ă��݃��档

AArch32�D��δ�@ʾMon��Hypģʽ�������֧Ԯ��ݕ�������R13��R14����ͬ������ģʽ��

��Cortex-A�У�����һ���cARM NEON SIMDָ�(��������)���P�Ă�ݕ���������������ʮ����128λԪ���ȵĕ�������ÿ�����������ɶ�ַ���ֽM���p�ֽM�����ֽM����NEONָ���λԪ�M�����ֽM��֧Ԯ�������I��

����ģʽ

�@�ɂ��ܘ��Į���ģʽ���ஔ��IJ�����߾�֧Ԯ�Ȳ��c�ⲿ����������ϵ�y�¼����ⲿ��߅�Д������С�

ARMv7-M֧Ԯ�c���y�������O����Ƶ�ģ�ͣ������ⲿ�Д�քe�^����̎����ʽλַ���������������

AArch32 ֧Ԯ��ģ�̈́t����f��ARM�ܘ�������ֻ�а˂��Ъ��������Į�����͡������������Ɉ��е�ָ���ͨ����ֱ���B�����m�Į���̎����ʽ�ķ�ָ֧��H֧Ԯ�� ���ⲿ�Д���Դ��FIQ��IRQ��һ��ֻ����һ���߃��ȵ��Д��B����FIQ�������t�B����IRQ���༴ϵ�y�������ܛ�w������������ͬ�F����ϵ�y����Ҋ �ģ��������Â��e����λַ�M�г�ʽ�OӋ��Vectored Interrupt Controller(VIC)��

�S�� Cortex-Aϵ�y��������ARM֮Generic Interrupt Controller(GIC)�ܘ��Ę˜��Д��������GIC�������S�����w�Д��ARM���ĵăɂ��Д�ݔ��(FIQ��IRQ)֮�g�Ľ��档���̎�탞�� ���ěQ�������ڡ����e�Д�����/ͣ�ú͓��Z��

ָ�

ARMָ���25��ǰ��ARM1�״��Ƴ����ѽ��^�S�����M��Cortex-A̎�������H��֧Ԯ�ɂ�ָ���ÿ��ָ������S�����졣

.ARMָ�

ARM ָ��Ե�һ��ARM̎������֧Ԯ��ԭʼָ�����A�����ѽ��^������졣���load-storeָ����Ⱥ�����ָ��Ⱥ�M���������Y��̎�����惦���� ȡ��ϵ�y���Ƽ������������F����ARMָ����и�Ч�ܣ��ҷ����V������ָ��е�����ָ����Թ̶��L�ȵ�32λԪ�ֽM���a�����ֽM߅���회��R��

.Thumbָ�

Thumb ָ���ARMָ����Ӽ�������ÿ��ָ������a��16λԪ�İ��ֽM������ֽM߅���회��R��Thumbָ���ԭʼ�����Ǟ����ھ��gC֮ĸ��A�Z�� �r���sС����ָ��Ĵ�С����˸��Ƴ�ʽ�a���ܶȡ�ָ��sС������ָ���Ŀ�ȡ�Ѓȿɷ������ָ����Ҳ�����ڏ�ָ���ȡ�Ȉ��С�

.�M�ASIMD���켯

�M�ASIMD���켯(Advanced SIMD Extensions)��Q��NEON���Ǵ��͵�ָ������������앺�����M���ṩSIMD����̎�����ܡ�

.�������c(VFP)

VFPָ����cNEON��ͬ�Ă�ݕ������ψ��У�����ṩ��Ч�ܵ�IEEE-754���݆�һ�c�p�ؾ��ʸ��c���I��

.Thumb-2���g

Thumb-2�����켯�����Q����ARMv6T2(���ȳ��F��ARM1156T2-S̎����)���뵽Thumbָ��ȡ�������L�ȵ�ָ����Y��Thumb�ij�ʽ�a�ܶ��cARMָ����^��Ч���c���ԡ�

�� ��ʹ����������Cortex-M�������M���_�l����ԓ����Thumb-2����Ϥ���@Щ��ʽ�a�ڏ�С(Cortex-M0��Cortex-M0+)�� ��(Cortex-M7)�ĸ��N�Ӽ��ЃH֧ԮThumb-2���D�Ƶ�Cortex-A̎�������ܞ��ʽ�a�����_���S������ԡ�

һ����f������ᘌ�Cortex-A̎�������g�ĸ��A��ʽ�a����Thumb(��Thumb-2)��Ŀ�ˡ���˾��g�ˆT�ɫ@�ô�����ɣ����ж����x���º����x����Ҫʹ�õ�ָ���ᘌ���ʽ�a���g�M�о��g�cᘌ�Ч���M�о��g�ɷN��r���F�ߵIJ��

ARMָ�ͨ�����ڱ��Ҫ�_����Ч�ܵij�ʽ�a�^�Ρ��@Щ�^���Еr���ڽM�g�����քӾ��a����ARMָ�ͨ�����Ǻõ��x��

NEONָ��������ж�N��ʽ��ȡ��

.�г�ʽ��֧Ԯ��Ҋ�Ĕ��W�c�������ܼ����㷨��

.���g��֧Ԯ�����ăȲ����ܼ������S��Cֱ�Ӵ�ȡ������NEONָ����^�@�N������NEON���I�����Ա����ķ�ʽ�cC��ʽ�a���e̎����

.NEON��ֱ���ڽM�g�����քӈ��С�

.���g����֧Ԯ������·���Ԅ�������ֻҪ��ѭһЩ���ε�ָʾ��������ʽ�a����ʹ�����@���s�Ļ�·�����g��Ҳ����Ч���м���������

���ʹ������ϤARMv7-A̎��������ԓҲ��ע�ARMv8-A����һЩ�~���ָ�

.�ܴa���g����ģ�M(Cryptographic Extensions)

�@Щָ���ARMv8-A�¼��룬Ŀ���Ǟ�����Ч������Ҋ�ļ��ܹ��ܽ����^�K���㷨���@Щ��������NEON��ݕ��������\����

.Load-Acquire��Store-Release

�@Щ��ָ�����C++11�惦�������Z�������������gЧ�ʡ�Ҳ���Á�p�ٌ��Y�ςȴ惦�������������֜p���c�����P�Ĺ�������

߀��һЩ�����c���c������ָ�����P��С�����졣

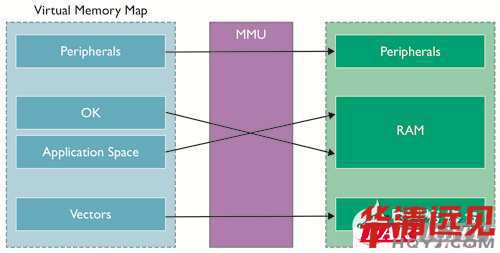

̓�M�惦��֧Ԯ

֧Ԯ����̓�M�惦���h����ARMv8-A��Ҫ����֮һ�������^�@헹��ܣ��@Щ�b�ò���֧ԮLinux��Android��ƽ�_���Iϵ�y����ˣ�̓�M�惦�����ܽ���Ҳ�����@Щ�������M���x��r���P�I�ėl����

̓�M�惦���h�������Iϵ�y�����惦���r�������ԣ�����ʹ���e̎������ӑB����ѯB�^�����Â��e�ij�ʽ�a���Y�υ^��ҕ��Ҫ���ⲿ������g�Ȳ����ⲿ�M�з�퓣����e��ʹ����̎��������ԙzҕ��ȫ��ͬ��ϵ�y�惦�����ÈD��

��l�]���ã�̓�M�惦����̎��������l��ÿ��λַ�ϼ�����“�D�g”����D7��ʾ��ܛ�w����“̓�Mλַ���g”���У�߀��һ������惦�������Ԫ�ą^�K�������D�g�錍�wλַ���g��

�D7��̓�M�惦��

����ʹ���Iϵ�y�������ƴ�ȡ���ȃ��ݣ���ᘌ�ϵ�y�ȵĸ��ʹ���߹��������Iϵ�y���������µ�̓�M�惦�����ÈD��ÿ헹����ɮ���ϵ�y��Ψһ�Ĺ��������Լ���̓�M�惦�����g�Ȉ��С�ֻ�����Iϵ�y֪��������ʽ�a���Y�υ^���ⲿ���w�惦���ȵČ��wλ�á�

���ГQ�����r�����Iϵ�y������һ��΄վ��������O���惦�������Ԫ���Ԇ��Â��빤�����õij�ʽ�a���Y�ϣ�ͬ�r���������Ĵ惦�����r�o����ȡ����˿ɏ��ƅ^�ֹ������鰲ȫ�ҏ��Ե�ϵ�y�ı�ҪԪ�ء�

�� ̎�����ṩ�����f����ARM̎�����ȵĴ惦�������Ԫʹ�ñ������ⲿ�惦���е�“��퓱�”�������Y�ρ펧�Ӽ������D�g��ϵ�y���϶�헼ѻ����I(���磬�� ��Translation Lookaside Buffers���Q��TLB���ܞ��ʹ���^���D�g������ȡ���Ԝp���xȡ��퓱��Ĺ�����)���ɱM���sС�D�g̎������Ĺ�������

��ARMv7-M��ARMv7-A��ܛ�w�D��

�����ĸ��Aܛ�w���Ҫ���ε����¾��g�����Ѕ^���ܛ�w�t�Ԕ��ע�⣺

.���ó�ʽ�a����������̎����ʽ

���ʹ�����Iϵ�y���@���ֵĹ����������Iϵ�y���ṩ�Ĺ��߁�̎����������r�£���Ҋ���Iϵ�y���B�Ӳ����^���_�W��ɢ�����b�ù������ṩ��

��ģʽ��^�������������Д�̎����ʽ�����Iϵ�yͬ�ӕ��ṩ���A�ܘ�������@���ֹ��������Ժ��ε����¾��g�����Д�̎����ʽ�����w��

.��߅�ӳ�ʽ

��RTOS�D�Ƶ�Linux�@Ķ��ƽ�_���Iϵ�y�r�����ó�ʽ�a����߅�ӳ�ʽ횸����_�ؼ��ԅ^����

.ϵ�y�M�B����

�� ��Cortex-M�cCortex-A���b�����ṩϵ�y�M�B�c���ƹ��ܴ�ȡ�������^��IJ��Cortex-M̎����ͨ���^������惦����ӳ�ĕ������� �O������ֱ���xȡ�����룬���_����Ҫ�Ĺ��ܡ�Cortex-A̎����(��Cortex-A32��֧Ԯ��AArch32���Р�B)�t���^“ϵ�y���ƅfͬ̎ ����”��֧Ԯ�O���������Ե�“�fͬ̎����15”�����������O������������ʹ�Ì��ٵ�ָ���M���xȡ�����롣�������Iϵ�y���е�ϵ�y�M�B���܄t������룬�� ����@���ֵĹ�����Ҳ�����f�����Iϵ�yͨ�����ṩ���ó�ʽ����(API)���������Ҫ��ʹ���߽����ȡ�Ĺ��ܡ�

.�R����ʽ�a

�� ���@�أ��R����ʽ�aҲ��eע�⡣��錑��R����ʽ�a������һ����Ҫԭ���Ǟ��˫@�øߵ�Ч�ܣ���˱��Ԕ�әz��@Щ���ܣ��_�����������ڴ�ȡ NEON��ijЩ����ָ����ܕr�ṩ��̎�����f�͵ąR����ʽ�a��ʹ��“Uniform Assembler Language(UAL)”�Z�����룬�t������ʽ�a�����ε���� R����ARM��Thumbָ�